I2S (Inter-IC Sound veya Integrated Interchip Sound), IC’ler arasında dijital ses verilerini iletmek için bir arayüz standardıdır. 2 set (sol ve sağ kanal) veri iletmek için bir sıra kullanır. 12s genellikle CD’nin PCM ses verilerini CD çaların DAC’ına iletmek için kullanılır. I2S, veri sinyalini ve saat sinyalini ayrı ayrı ilettiği için titreşim distorsiyonu çok azdır. 112S veri yoluna genel bakış

Ses verilerinin toplanması, işlenmesi ve iletilmesi multimedya teknolojisinin önemli bir parçasıdır. Dijital ses bantları ve dijital ses işlemcileri gibi çok sayıda dijital ses sistemi tüketici pazarına girmiştir. Ekipman ve üreticiler için standartlaştırılmış bir bilgi aktarım yapısı, sistemin uyarlanabilirliğini artırabilir. 12s (Inter— (Ses) veriyolu, Philips tarafından dijital ses aygıtları arasında ses verilerinin iletimi için formüle edilmiş bir veri yolu standardıdır Veri yolu, ses aygıtları arasında veri aktarımına adanmıştır ve çeşitli multimedya sistemlerinde yaygın olarak kullanılmaktadır. Ayrı kablolar boyunca saat ve veri sinyallerini iletme tasarımı benimsenmiştir Veri ve saat sinyallerini ayırarak, zaman farkının neden olduğu bozulma önlenir ve kullanıcılar için ses titremesine dirençli profesyonel ekipman satın alma maliyeti kaydedilir.

2 I2S veri yolu yapısı yapılandırması

WS sinyali değiştikçe, bir WSP darbe sinyali türetilir ve paralel kaydırma yazmacına girer, böylece çıkış verileri etkinleştirilir. Seri verilerin varsayılan girişi 0’dır, bu nedenle en az önemli bitten (LSB) sonraki tüm veriler 0’a ayarlanacaktır.

İlk WS sinyalinin değişmesiyle, WSP, SCK sinyalinin düşen kenarında sayacı sıfırlar. “Loutofn” kod çözücünün sayaç değerinin kodunu çözmesinden sonra, ilk seri veriler (MSB) SCK saat sinyalinin yükselen kenarında B1’e kaydedilir. Sayaç arttıkça, sonraki veriler sırayla saklanır. B2’den Bn’ye girin. Sonraki WS sinyali değiştiğinde, veriler WSP darbesinin değişikliğine göre sol (kanal) mandalına veya sağ (kanal) mandalına kaydedilir ve B2-Bn verileri temizlenir ve varsa sayaç sıfırlanır. Fazlalık veriler için, en önemsiz bitten sonraki veriler göz ardı edilecektir. Not: Kod çözücü ve sayaç (kesikli çizgi içindeki kısım) bir n-bit kaydırma yazmacı ile değiştirilebilir.

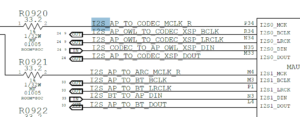

IIS veriyolu arabirimi, mikro kayıt ve taşınabilir uygulamaları gerçekleştirmek için harici bir 8/16 bit stereo ses çözme devresine (CODECIC) bağlanmak için bir kodek arabirimi olarak kullanılabilir. IIS veri biçimini ve MSB ・ Yaslanmış veri biçimini destekler. IIS veri yolu arabirimi, kesme modunu değiştirmek için ilk giren ilk çıkar kuyruğu FIFO’nun erişimi için bir DMA aktarım modu sağlar.Aynı anda veri gönderip alabilir veya yalnızca veri gönderip alabilir.

3 I2S veriyolu özellikleri

Philips’in 12s standardında, hem donanım arayüz özellikleri hem de dijital ses veri formatı belirtilmiştir.

I2S’nin 3 ana sinyali vardır

1. Bit saati (BCLK) olarak da adlandırılan seri saat SCLK, dijital ses verilerinin her bitine karşılık gelir, SCLK 1 darbeye sahiptir. SCLK’nin frekansı = 2X örnekleme frekansı X örnekleme bitleri.

2. Çerçeve saati LRCK (WS olarak da adlandırılır), sol ve sağ kanalların verilerini değiştirmek için kullanılır. “1” olan LRCK, sağ kanalın verilerinin iletildiği ve “0” sol kanalın verilerinin iletildiği anlamına gelir. LRCK’nin frekansı, örnekleme frekansına eşittir.

3. Seri veri SDATA, ikinin tamamlayıcısı olarak ifade edilen ses verileridir.

Bazen sistemleri daha iyi senkronize etmek için, örnekleme frekansının 256 katı veya 384 katı olan ana saat olarak da adlandırılan sistem saati (SysClock) olarak da adlandırılan başka bir MCLK sinyalinin iletilmesi gerekir.

Seri veri (SD)

I2S format sinyalinde kaç bit geçerli veri olursa olsun, verilerin en yüksek biti her zaman LRCK değişikliğinden sonra (yani bir çerçevenin başlangıcında) ikinci SCLK darbesinde görünür. Bu, alıcı ucun ve gönderen ucun efektif rakamlarını farklı kılar. Alıcı uç tarafından işlenebilecek etkin bit sayısı, ileten uçtan daha azsa, veri çerçevesindeki fazla düşük bitli veriden vazgeçebilir; alıcı uç, ileten uçtan daha etkili bitleri işleyebilirse, kalan bitleri kendi başına oluşturabilir. Bu senkronizasyon mekanizması, dijital ses ekipmanının ara bağlantısını daha rahat hale getirir ve verilerin yanlış hizalanmasına neden olmaz.

Teknolojinin gelişmesiyle birlikte, birleşik 12’ler arayüzü altında çeşitli farklı veri formatları ortaya çıktı. SDATA verilerinin LRCK ve SCLK’ye göre farklı konumlarına göre, sola dayalı (daha az kullanılan), 12s formatı (yani Philips tarafından belirtilen format) ve sağa dayalı (Japon formatı, normal format olarak da adlandırılır) olarak ayrılır.

Dijital ses sinyallerinin doğru iletimini sağlamak için, gönderici ve alıcı aynı veri formatını ve uzunluğunu kullanmalıdır. Tabii ki veri uzunluğu 12s formatında farklı olabilir.

Alan (kanal) seçimi (WS)

Komut seçim satırı, iletilmekte olan kanalı gösterir.

WS = 1, bu, doğru kanalın verilerinin iletildiği anlamına gelir.

WS = O, sol kanalın verilerinin iletildiği anlamına gelir.

WS, seri saatin yükselen veya alçalan kenarında değişebilir ve WS sinyalinin simetrik olması gerekmez. Bağımlı cihaz tarafında WS, saat sinyalinin yükselen kenarında değişir. WS, en yüksek bit iletiminden önce her zaman bir saat döngüsünü değiştirir, böylece bağımlı aygıt, iletilen seri verilerle senkronize olan zamanı alabilir ve alıcı uç, geçerli komutu depolayabilir ve sonraki komut için boş alan sağlayabilir.

Elektriksel özellikler:

Çıkış voltajı:

VK0.4V

VH> 2.4V giriş voltajı

VIL = 0.8V

VIH = 2.0V

Not: Bu, kullanılan TTL seviyesi standardıdır.Diğer IC’ler (LSI) popüler hale geldikçe, diğer seviyeler de desteklenecektir.

Zamanlama gereksinimleri

12s veriyolunda, herhangi bir cihaz gerekli saat sinyalini sağlayarak sistemin ana cihazı haline gelebilir ve bağımlı cihaz dahili saat sinyalini harici saat sinyali aracılığıyla alır, bu da ana cihaz, veri ve komut seçim sinyaline dikkat edilmesi gerektiği anlamına gelir. Toplam gecikme arasındaki yayılma gecikmesi esas olarak iki bölümden oluşur:

1. Harici saat ile ikincil cihazın dahili saati arasındaki gecikme

2. Dahili saat ile veri sinyali ve komut seçim sinyali arasındaki gecikme

Veri ve komut sinyallerinin girişi için, harici saatin ve dahili saatin gecikmesi baskın değildir, sadece etkin kurulum süresini (kurulum süresi) uzatır. Gecikmenin ana kısmı, gönderenin iletim gecikmesi ve alıcıyı ayarlamak için gereken süredir.

T, saat periyodudur, Tr, izin verilen minimum saat periyodudur, T> Tr, böylece gönderici ve alıcı, veri iletim hızı gereksinimlerini karşılayabilir.

Tüm veri hızları için, hem gönderen hem de alıcı sabit bir işaret-boşluk oranına sahip bir saat sinyali gönderir, bu nedenle tLC ve tHC, T ile tanımlanır. tLC ve tHC, sinyalin bağımlı cihaz tarafında tespit edilebilmesi için 0,35T’den büyük olmalıdır.

Gecikme (tdtr) ve en hızlı iletim hızı (Ttr tarafından tanımlanmıştır) ilişkilidir.Yavaş bir saat yükselen kenarında hızlı bir gönderen sinyali tdtr’nin tRC’yi aşmamasına ve bunu sıfır veya negatif yapmasına neden olabilir. Yalnızca tRC, tRCmax’tan (tRCmax>: 0.15T) büyük olmadığında, gönderen, thtr’nin Oo değerinden büyük veya ona eşit olmasını sağlayabilir.

Verilerin düşen kenarda kaydedilmesine izin vermek için, saat sinyalinin yükselen kenarı ve T ile ilişkili zaman gecikmesi, alıcı uca yeterli kurulum süresi vermelidir.

Veri kurulum süresi (kurulum süresi) ve tutma süresi (bekleme süresi), belirlenen alıcının kurulum süresi ve tutma süresinden daha az olamaz.